ESTUDIANTE: SERGIO ANDRÉS GARZÓN AGUDELO

20171005080

20171005080

En esta práctica, se quiere realizar visualización dinámica en solo display 7 segmentos, y con una memoria ROM, un decodificador, un multiplexador y un demultiplexador; donde se visualiza los últimos 4 dígitos del código de la Universidad, en este caso, mi código termina en 5084. El circuito a implementar será el siguiente:

ROM

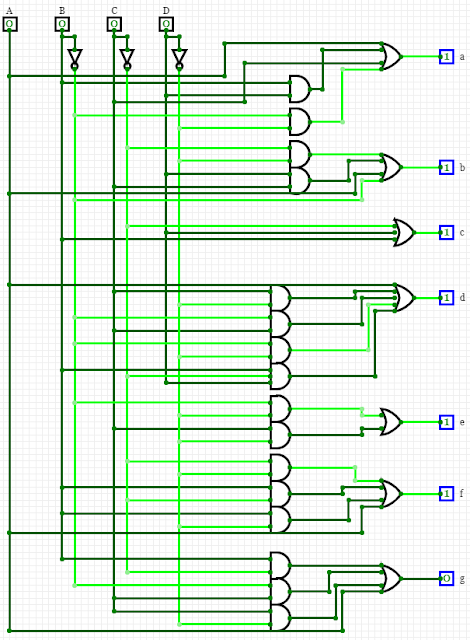

Para la memoria ROM, se crea primero el decodificador, para luego implementar las compuertas OR (en esta ROM no es necesario las compuertas OR, ya se verá por qué):

Luego de crear el decodificador, se procede a conectar las salidas haciendo la siguiente secuencia:

| S3 | S2 | S1 | S0 | A | B | C | D | NÚMERO |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 5 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 8 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Tabla 1. Secuencia ROM

Donde el circuito correspondiente es el siguiente:

Y como se mencionó antes, no son necesarias las compuertas OR, ya que solo hay una entrada por salida, no varias, por ende, son salidas directas.

BCD@7SEGMENTOS

Este decodificador es el mismo usado en la Práctica 7, por ende, solo pondré el circuito del mismo, sin poner los mapas de Karnaugh ni la Tabla de verdad:

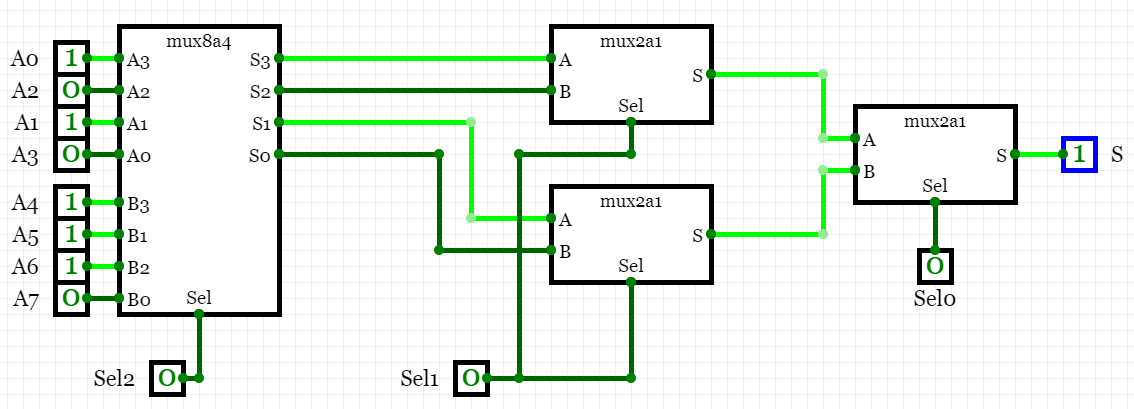

MULTIPLEXADOR 8 A 1

Para esta práctica, es necesario un multiplexador 8 a 1, donde las entradas van a ir conectadas a las salidas del decodificador BCD@7Segmentos (en el multiplexador va a sobrar una entrada, donde le pondremos un "0" lógico), e irá una salida hacía el demultpliexador 8 a 1. Los selectores de este multiplexador son 3, debido a la regla de Número de entradas/Número de salidas= 2^Número de selectores, que en este caso, sería 8/1=2^3, donde el número de selectores es 3, e irán conectados a un contador de 3 bits (proporcionado por el monitor de la clase). El circuito del multiplexador es el siguiente:

La construcción de este multiplexador se verá paso a paso en el video.

DEMULTIPLEXADOR 1 A 8

Este demultiplexador va conectado en la entrada con la salida del multiplexador, y donde sus salidas, serán visualizadas en el Display. Este demultiplexador también se compone de 3 selectores, y sigue una regla similar al multiplexador, donde se intercambia el orden de salidas y entradas, así: Número de Salidas/Número de Entradas=2^Número de Selectores, donde 8/1=2^3, siendo el número de selectores 3, que van conectados al contador también. El circuito es el siguiente:

Al igual que con el multiplexador, la construcción de este demultiplexador se verá paso a paso en el video.

El circuito total de esta práctica se puede observar a continuación:

Cabe resaltar, que en este circuito, debido a que el contador no tiene un reset, habrá un punto muerto cuando llegue al número 7, debido a que como solo hay 7 salidas funcionando para el display, no habrá nada para ese número 7.

ANÁLISIS DE RESULTADOS

El video del montaje está aquí:

Y el montaje del circuito estará a continuación:

CONCLUSIONES

- Debido al simulador, el reloj no puede hacer visualizar correctamente en el display el número deseado, por lo que hará un conteo muy despacio por cada salida del contador, y no hará que sea vea el efecto de que el display parezca estar siempre encendido.

- Las memorias ROM son muy útiles a la hora de querer aplicar cualquier cosa en el sentido de alguna secuencia de números, donde si es mas grande, se crea el decodificador de la ROM mas grande, así pudiendo ser usada para muchos diseños.

No hay comentarios:

Publicar un comentario