Para la práctica 13, se quiere comparar el decodificador de Binario a 7 segmentos, donde se quiere visualizar del 0 al 9, y después del 9, de la A a la F (siendo b y d mostradas en minúsculas). Se hizo uno con compuertas lógicas, y otro con el lenguaje Verilog.

DECODIFICADOR CON COMPUERTAS

La tabla de verdad del decodificador es la siguiente:

Donde la reducción de la tabla se hace mediante mapas de Karnaugh, que tiene sus respectivas ecuaciones:

Y el circuito equivalente es el siguiente :

|

| Imagen 2. Circuito del deco. |

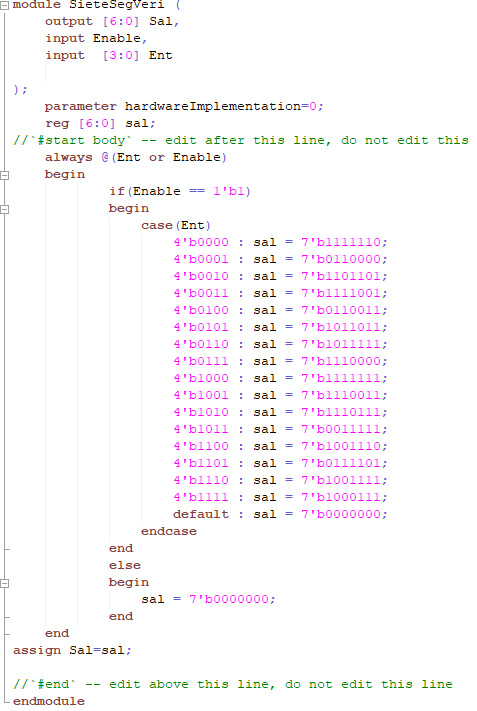

El bloque creado para Verilog es el siguiente:

Donde el código del bloque en Verilog es el siguiente:

Donde la conexión del bloque es la siguiente:

Ahora, se muestran a continuación 2 imágenes de la memoria de cada deco:

En las imágenes, el consumo de recursos es el mismo, pero, si se realizara un proyecto más extenso, a veces es recomendable usar Verilog para los componentes, puesto que van a consumir una menor cantidad de recursos de Psoc.

Los archivos tienen como nombre Lab13 y Labalgo, donde el Lab13 es la implementación del deco con verilog, y el otro la implementación del deco con compuertas.

https://mega.nz/file/RTw3QZyC#vExqV_fEeCOZcp9PKg43m4KemKAS_o-UWbz_A3rBw0U

(LAB 13)

(Labalgo)